# Section 3. System Board I/O Controllers

(

| Keyboard/Mouse Controller                            | . 3-3          |

|------------------------------------------------------|----------------|

| Keyboard Password Security                           | . 3 <b>-</b> 3 |

| Keyboard Controller Command and Status Bytes         | . 3-5          |

| Keyboard/Mouse Programming Considerations            | . 3-9          |

| Mouse/System Timings                                 | 3-10           |

| Signals                                              | 3-12           |

|                                                      |                |

| Video Subsystem                                      | 3-14           |

| VGA Components                                       | 3-17           |

| BIOS ROM                                             | 3-18           |

| Support Logic                                        | 3-18           |

| Video Graphics Array Major Components                | 3-18           |

| Modes of Operation                                   | 3-22           |

| Display Support                                      | 3-23           |

| Video Subsystem Programmable Option Select           | 3-24           |

| Alphanumeric Modes                                   | 3-25           |

| Graphics Modes                                       | 3-28           |

| Video Memory Organization                            | 3-35           |

| Video Memory Read/Write Operations                   | 3-50           |

| Registers                                            | 3-53           |

| General Registers                                    | 3-54           |

| Sequencer Registers                                  | 3-58           |

| CRT Controller Registers                             | 3-64           |

| Graphics Controller Registers                        | 3-79           |

| Attribute Controller Registers                       | 3-87           |

| VGA Programming Considerations                       | 3-93           |

| Video Digital-to-Analog Converter (Video DAC)        | 3-101          |

| Diskette Drive Controller                            | 3-111          |

| Registers                                            | 3-112          |

| Diskette Drive Controller Programming Considerations | 3-115          |

| Command Format                                       | 3-118          |

| Command Status Registers                             | 3-128          |

| Signal Descriptions                                  | 3-131          |

|                                                      | 3-134          |

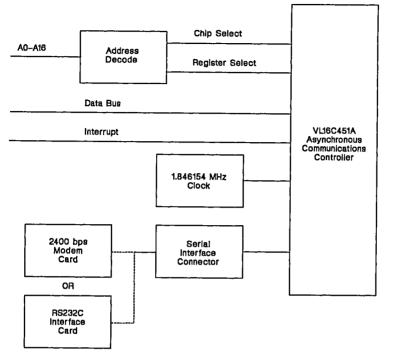

| Serial Port Controller                               | 3-135          |

| Communications Application                           | 3-136          |

| Programmable Baud-Rate Generator                     | 3-137          |

| Registers                                            | 3-137          |

|                                                      | 3-147          |

| Signal Descriptions                                  | 3-147          |

|                                                      | 3-148          |

|                                                      | 3-149          |

| ·                                                    |                |

| Parallel Port Programmable Option Select            | 3-150 |

|-----------------------------------------------------|-------|

| Parallel Port Controller Programming Considerations | 3-151 |

| Parallel Port Timing                                | 3-154 |

| Signal Descriptions                                 | 3-154 |

| Connector                                           | 3-155 |

| Memory                                              | 3-156 |

| Read-Only Memory (ROM)                              | 3-156 |

| Random Access Memory (RAM)                          | 3-156 |

| Complementary Metal Oxide Semiconductor RAM         | 3-158 |

| CMOS RAM Configuration                              | 3-162 |

| Miscellaneous System Ports                          | 3-165 |

| System Control Port B (Hex 0061)                    | 3-165 |

| RTC/CMOS and NMI Mask (Hex 0070)                    | 3-166 |

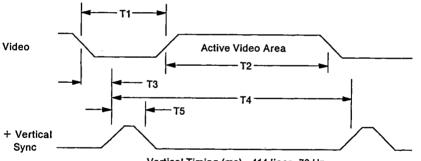

| System Control Port A (Hex 0092)                    | 3-167 |

|                                                     | 0-10/ |

(

· (

. (

# **Keyboard/Mouse Controller**

The keyboard/mouse controller uses an Intel 8042 microprocessor. The keyboard is connected to the left-most of the two controller connectors in the rear of the system unit. This connector is dedicated to the keyboard.

The keyboard controller receives the serial data, checks the parity, translates keyboard scan codes (see "Keyboard Controller Command and Status Bytes" on page 3-5), and presents the data to the system as a byte of data at I/O address hex 0060. The interface can interrupt the system when data is available or can wait for polling from the microprocessor.

I/O address hex 0064 is the command/status port. When the system reads I/O address hex 0064, it receives status information from the keyboard controller. When the system writes to the port, the keyboard controller interprets the byte as a command.

### **Keyboard Password Security**

The keyboard controller provides for a password security mechanism. Three commands are available regarding password operation:

- A4 Test Password Installed

- A5 Load Security

- A6 Enable Security.

The system microprocessor can issue a Test Password Installed command to determine if a password is currently installed. This feature allows the controlling program to decide whether or not to write over the existing password.

The system microprocessor can issue a Load Security command and set a password in the keyboard controller at any time. Any existing password is lost, and the new password becomes the active password. The password must be installed in scan code format.

The system microprocessor must issue the Enable Security command to set the keyboard controller into Secure mode. At this point the keyboard controller does not pass any information along to the system microprocessor. The keyboard controller intercepts the keyboard data stream, continuously comparing it to the installed password pattern. Until a match is encountered, no keyboard or mouse data is passed to the system microprocessor. When a match occurs, the state of the keyboard controller is restored and data is allowed to pass to the system microprocessor.

The password can be changed as often as the user chooses. No command to verify the installed password is provided. No commands are accepted by the keyboard controller when keyboard security is active.

í

### **Keyboard Controller Command and Status Bytes**

### Keyboard Controller Command Byte (Hex 0064, Write)

Figure 3-1 and Figure 3-2 on page 3-6 show the keyboard controller command and status bytes:

| Figure<br>Bit                                                         | 3-1. Keyboard Controller Com<br>Function | mand B | yte, Port Hex 0064 Write                                                                           |  |

|-----------------------------------------------------------------------|------------------------------------------|--------|----------------------------------------------------------------------------------------------------|--|

| 7                                                                     | Reserved = $0$                           |        |                                                                                                    |  |

| 6                                                                     | IBM Keyboard Translate Mode              | 1=     | Translate incoming scan codes to Scan Codes to Scan Code Set 1*                                    |  |

|                                                                       |                                          | 0=     | No translation                                                                                     |  |

| 5                                                                     | Disable Mouse                            | 1=     | Drive clock low, disabling<br>mouse interface                                                      |  |

|                                                                       |                                          | 0=     | Drive clock high, enabling<br>mouse interface                                                      |  |

| 4.                                                                    | Disable Keyboard                         | 1=     | Drive clock low, disabling<br>keyboard interface                                                   |  |

|                                                                       |                                          | 0=     | Drive clock high, enabling<br>keyboard interface                                                   |  |

| 3                                                                     | Reserved = $0$                           |        |                                                                                                    |  |

| 2                                                                     | System Flag                              |        | Placed in the system flag<br>bit of the keyboard<br>controller status register                     |  |

| 1                                                                     | Enable Mouse Interrupt                   | 1=     | Keyboard controller<br>generates an interrupt<br>when mouse data is<br>written to output buffer    |  |

| 0                                                                     | Enable Keyboard Interrupt                | 1=     | Keyboard controller<br>generates an interrupt<br>when keyboard data is<br>written to output buffer |  |

| * Used on the IBM Personal Computer and the IBM Personal Computer XT. |                                          |        |                                                                                                    |  |

### Keyboard Controller Status Byte (Hex 0064, Read)

Figure 3-2 shows the keyboard controller status byte:

| Figure<br>Bit | 3-2. Keyboard Controller Status Byte, Port Hex 0064 Read<br>Function |

|---------------|----------------------------------------------------------------------|

| 7             | Parity Error                                                         |

| 6             | General Time Out                                                     |

| 5             | Mouse Output Buffer Full                                             |

| 4             | Inhibit Switch                                                       |

| 3             | Command/Data                                                         |

| 2             | System Flag                                                          |

| 1             | Input Buffer Full                                                    |

| 0             | Output Buffer Full                                                   |

#### Input Buffer

The input buffer (hex 0060) is an 8-bit write-only register. When the input buffer is written, a flag is set that indicates a data write. Data written to the input buffer is sent to the keyboard unless the keyboard controller is expecting a data byte following a keyboard controller command. Data should be written to the keyboard controller input buffer only if Input Buffer Full (bit 1) in the status byte (hex 0064) is equal to 0.

#### **Output Buffers**

The output buffer (hex 0060) is an 8-bit read-only register. When the output buffer is read, the keyboard controller uses it to send information to the system microprocessor. The information can be scan codes from the keyboard, data from a mouse, or data bytes that result from a command from the system microprocessor.

#### **Keyboard Controller Commands**

A command is a byte written to the keyboard controller through I/O address hex 0064. The following are the recognized keyboard controller commands (hex values).

- **20-3F** Read Keyboard Controller RAM Bits D5-D0 specify the address.

- 20 Read Keyboard Controller Command Byte The keyboard controller puts the command byte in its output buffer (hex 0060).

- 60-7F Write Keyboard Controller RAM Bits D5-D0 specify the address.

- 60 Write Keyboard Controller Command Byte The keyboard controller puts the next byte of data written to I/O address hex 0060 in its command byte.

- A4 Test Password Installed This command checks for a password installed in the keyboard controller. The result, hex FA (password installed) or hex F1 (password not installed), is placed in the output buffer (I/O address hex 0060 and IRQ01).

- A5 Load Security This command initiates the password load procedure. The keyboard controller inputs from the data port until it detects a 0, which terminates password entry.

- A6 Enable Security This command enables the keyboard controller security feature. This command is valid only when a password pattern is currently loaded into the keyboard controller.

- A7 Disable Mouse Interface -- This command sets bit 5 of the keyboard controller command byte to 1, driving the clock line low which disables the mouse interface. Data is not sent or received.

- A8 Enable Mouse Interface This command clears bit 5 of the keyboard controller command byte to 0, which enables the mouse interface.

- A9 Interface Test This command causes the keyboard controller to test the mouse clock and data lines. The result is placed in the output buffer (I/O address hex 0060 and IRQ01) as shown in Figure 3-3.

| Figure 3-3. Command A9 Test Results |                                 |  |  |  |  |

|-------------------------------------|---------------------------------|--|--|--|--|

| Test Result (hex)                   | Meaning                         |  |  |  |  |

| 00                                  | No error was detected.          |  |  |  |  |

| 01                                  | Mouse clock line is stuck low.  |  |  |  |  |

| 02                                  | Mouse clock line is stuck high. |  |  |  |  |

| 03                                  | Mouse data line is stuck low.   |  |  |  |  |

| 04                                  | Mouse data line is stuck high.  |  |  |  |  |

AA Self Test – This command causes the keyboard controller to perform internal diagnostic tests. Hex 55 is placed in the output buffer (I/O address hex 0060) if no errors are detected. Interface Test – This command causes the keyboard controller to test the keyboard clock and data lines. The result is placed in the output buffer (I/O address hex 0060 and IRQ01) as shown in Figure 3-4 on page 3-8.

| Figure 3-4. Command AB Test Results Test Result (hex) Meaning |                                    |  |  |  |  |

|---------------------------------------------------------------|------------------------------------|--|--|--|--|

|                                                               | meaning                            |  |  |  |  |

| 00                                                            | No error was detected.             |  |  |  |  |

| 01                                                            | Keyboard clock line is stuck low.  |  |  |  |  |

| 02                                                            | Keyboard clock line is stuck high. |  |  |  |  |

| 03                                                            | Keyboard data line is stuck low.   |  |  |  |  |

| 04                                                            | Keyboard data line is stuck high.  |  |  |  |  |

#### AC Reserved

ΔB

- AD Disable Keyboard Interface This command sets bit 4 of the keyboard controller command byte to 1, driving the clock line low which disables the keyboard interface. Data will not be sent or received.

- AE Enable Keyboard Interface This command clears bit 4 of the keyboard controller command byte to 0, which enables the keyboard interface.

- **C0 Read Input Port** This command causes the keyboard controller to read its input port and place the data in the output buffer (hex 0060). This command should only be used if the output buffer is empty.

(

ļ

- C1 Poll Input Port Low Port 1 bits 0-3, in status bits 4-7.

- C2 Poll Input Port High Port 1 bits 4-7, in status bits 4-7.

- **D0 Read Output Port** This command causes the keyboard controller to read its output port and place the data in the output buffer (hex 0060). This command should only be used if the output buffer is empty.

- D1 Write Output Port The next byte of data written to I/O address hex 0060 is placed in the keyboard controller output port.

- Note: Bit 0 of the keyboard controller output port is connected to System Reset. This bit should not be written low.

- Note: System Control Port A should be used to set Alternate Gate A20 instead of writing to the output port. See page 3-167.

- D2 Write Keyboard Output Buffer The next byte written to the input buffer (hex 0060), is written to the output buffer (hex 0060) as if initiated by a device. An interrupt occurs if the interrupt is enabled in the command byte.

- D3 Write Mouse Output Buffer The next byte written to the input buffer (hex 0060) is written to the output buffer (hex 0060) as if initiated by a device. An interrupt occurs if the interrupt is enabled in the command byte.

- D4 Write to Mouse The next byte written to the input buffer (hex 0060) is transmitted to the mouse.

- E0 Read Test Inputs This command causes the keyboard controller to read its T0 and T1 inputs. This data is placed in the output buffer. Data bit 0 represents T0 and data bit 1 represents T1.

- F0-FF Pulse Output Port Bits 0 through 3 of the keyboard controller output port can be pulsed low for approximately 6 microseconds. Bits 0 through 3 of this command indicate which bits are to be pulsed. A 0 indicates that the bit should be pulsed. A 1 indicates the bit should not be modified.

- Note: Bit 0 of the keyboard controller output port is connected to System Reset. Pulsing of this bit resets the system microprocessor.

### **Keyboard/Mouse Programming Considerations**

The following are some programming considerations for the keyboard/mouse controller.

- Status register (I/O address hex 0064) can be read at any time.

- Output buffer (I/O address hex 0060) should be read only when the Output Buffer Full (bit 0) in the status register is 1.

- The Mouse Output Buffer Full (bit 5) in the status register indicates that the data in the output buffer (hex 0060) came from the mouse. This bit is valid only when the Output Buffer Full (bit 0) is 1.

- The output buffer (hex 0060) and status register (hex 0064) should be written only when the input Buffer Full (bit 1) and the Output Buffer Full (bit 0) are 0s.

- The devices connected to the keyboard controller should be disabled before initiating a command that generates output. If output is generated, any value in the output buffer is overwritten.

# **Mouse/System Timings**

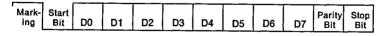

Data transmissions to and from the mouse connector consist of an 11-bit data stream sent serially over the data line. Figure 3-5 on page 3-10 shows the function of each bit.

| Figure<br>Bit | 3-5. Mouse Data Stream Bit Definitions<br>Function |

|---------------|----------------------------------------------------|

| 11            | Stop Bit (always 1)                                |

| 10            | Parity Bit (odd parity)                            |

| 9             | Data Bit 7 (most-significant)                      |

| 8             | Data Bit 6                                         |

| 7             | Data Bit 5                                         |

| 6             | Data Bit 4                                         |

| 5             | Data Bit 3                                         |

| 4             | Data Bit 2                                         |

| 3             | Data Bit 1                                         |

| 2             | Data Bit 0 (least-significant)                     |

| 1             | Start Bit (always 0)                               |

#### System Receiving Data

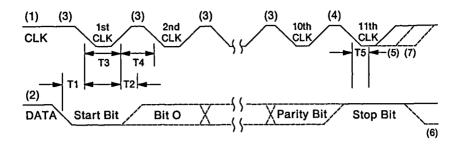

The following describes the typical sequence of events that takes place when the system is receiving data from the mouse. Figure 3-6 on page 3-11 shows a graphic representation of the timing relationships.

- 1. The mouse checks the clock line. If the line is inactive, output from the mouse is not allowed.

- 2. The mouse checks the data line. If the line is inactive, the mouse receives data from the system.

- 3. The mouse checks the clock line at intervals not exceeding 100 microseconds during transmission. If the system is holding the clock line inactive, the transmission is terminated. The system can terminate transmission anytime during the first 10 clock cycles.

- 4. A final check for terminated transmission is performed at least 5 microseconds after the 10th clock.

- 5. The system can hold the clock line inactive to inhibit the next transmission.

- 6. The system can set the data line inactive when it has data to transmit to the mouse. The start bit (always 0) sets the data line inactive.

(

7. The system raises the clock line to allow the next transmission.

| Figurø | 3-6. Receiving Data Timings<br>Timing Parameter                                              | Min/Max<br>(microseconds) |

|--------|----------------------------------------------------------------------------------------------|---------------------------|

| Т1     | Time from DATA transition to falling edge of CLK                                             | 5 / 25                    |

| T2     | Time from rising edge of CLK to DATA transition                                              | 5 / T4 - 5                |

| Т3     | Duration of CLK inactive                                                                     | 30 / 50                   |

| T4     | Duration of CLK active                                                                       | 30 / 50                   |

| T5     | Time to mouse inhibit after clock 11 to ensure the mouse does not start another transmission | >0 / 50                   |

#### System Sending Data

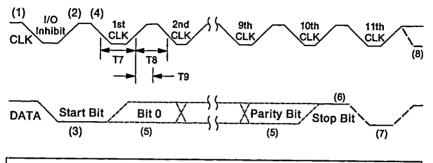

The following describes the typical sequence of events that takes place when the system is sending data to the mouse. Figure 3-7 on page 3-12 shows timing relationships.

- 1. The system checks for a mouse transmission in process. If a transmission is in process and beyond the 10th clock, the system must receive the data.

- 2. The mouse checks the clock line. If the line is inactive, an I/O operation is not allowed.

- 3. The mouse checks the data line. If the line is inactive, the system has data to transmit. The start bit (always 0) sets the data line inactive.

- 4. The mouse sets the clock line inactive. The system then places the first bit on the data line. Each time the mouse sets the clock line inactive, the system places the next bit on the data line until all bits are transmitted.

- 5. The mouse samples the data line for each bit while the clock line is active. Data must be stable within 1 microsecond after the rising edge of the clock line.

- 6. The mouse checks for a positive-level stop bit after the 10th clock. If the data line is inactive, the mouse continues to clock until the

data line becomes active, clocks the line-control bit, and at the next opportunity sends a Resend command to the system.

- 7. The mouse sets the data line inactive, producing the line-control bit.

- 8. The system can set the clock line inactive, inhibiting the mouse.

| Figure | e 3-7. Sending Data Timings<br>Timing Parameter                                          | Min/Max<br>(microseconds) |

|--------|------------------------------------------------------------------------------------------|---------------------------|

| T7     | Duration of CLK inactive                                                                 | 30 / 50                   |

| T8     | Duration of CLK active                                                                   | 30 / 50                   |

| T9     | Time from inactive to active CLK transition, used<br>to time when the mouse samples DATA | 5 / 25                    |

# Signals

The keyboard and mouse signals are driven by open-collector drivers pulled to 5 V dc through 4.7K ohm resistors. Figure 3-8 shows the characteristics of the signals.

| Figure 3-8. Keyboard/N<br>Signal | louse Signals           |         |

|----------------------------------|-------------------------|---------|

| Sink Current                     | 20 mA                   | Maximum |

| High-level Output Voltage        | + 5.0 V dc minus pullup | Minimum |

| Low-level Output Voltage         | + 0.5 V dc              | Maximum |

| High-level Input Voltage         | + 2.0 V dc              | Minimum |

| Low-level Input Voltage          | + 0.8 V dc              | Maximum |

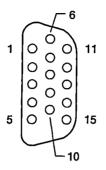

### Connector

The keyboard and the mouse connectors are 6-pin miniature DIN connectors. Figure 3-9 shows the voltages and signals assigned to the keyboard/mouse connectors.

| Figure | 3-9. Keyboar<br>Assignm | d/Mouse Connectors Voltage and Signal<br>ents |

|--------|-------------------------|-----------------------------------------------|

| Pin    | 1/0                     | Signal Name                                   |

| 1      | I/O                     | Data                                          |

| 2      | NA                      | Ground                                        |

| 3      | NA                      | Ground                                        |

| 4      | NA                      | +5 V dc                                       |

| 5      | 1/0                     | Clock                                         |

| 6      | NA                      | Ground                                        |

# Video Subsystem

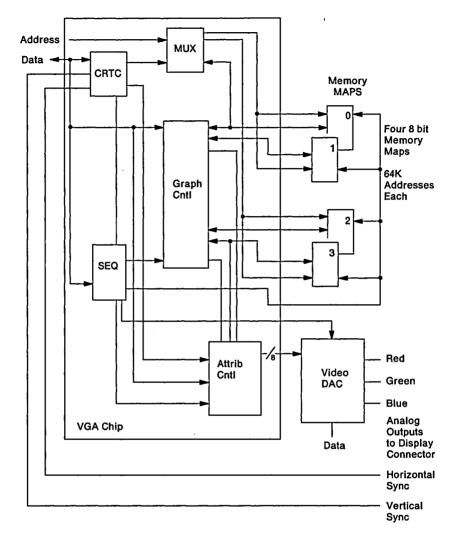

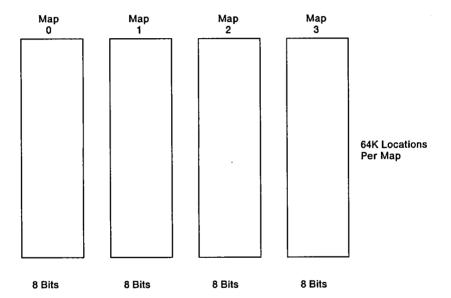

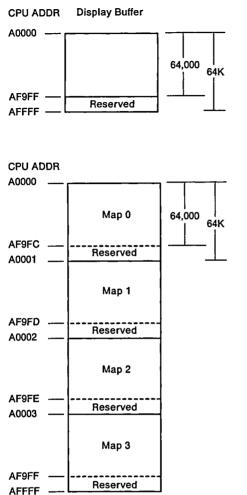

The system video is generated by the IBM Video Graphics Array (VGA) and its associated circuitry. The associated circuitry consists of the video memory and a video digital-to-analog converter (DAC). The 256KB of video memory consists of four 64KB by 8 memory maps. The red, green, and blue (RGB) outputs from the video DAC drive analog displays with 31.5 KHz horizontal deflection.

All video modes available on the IBM Monochrome Display Adapter, IBM Color/Graphics Monitor Adapter, and IBM Enhanced Graphics Adapter are supported. All video modes supported by the video subsystem are available on all of the supported analog displays. Colors will be displayed as shades of gray when the monochrome analog display is used.

The modes available are:

- 640 by 480 graphics in both 2 and 16 colors

- 720 by 400 alphanumeric in both 16-color and monochrome

- 360 by 400 16-color alphanumeric

- 320 by 200 graphics with 256 colors.

In addition, all 200 line modes are double-scanned by the video subsystem and displayed as 400 lines on the display. This means that each 1-PEL-high horizontal scan line is displayed twice on the display.

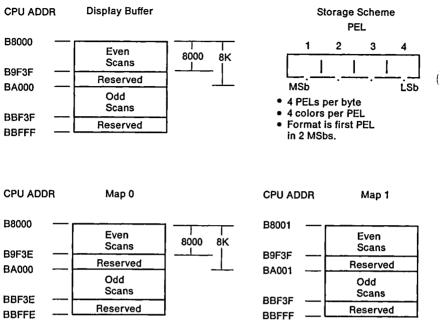

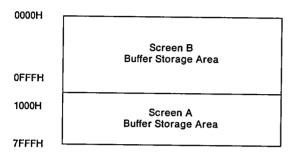

The VGA interfaces with the system microprocessor and video memory. All data passes through the VGA when the system microprocessor writes to or reads from video memory. The VGA controls the arbitration for video memory between the system microprocessor and the cathode ray tube (CRT) controller function contained within the VGA. Programs do not need to wait for horizontal retrace to update the display buffer. The system microprocessor receives better performance when accessing the display buffer during non-active display times because there is less interference from the CRT controller. Video memory addressing is controlled by the VGA. The starting address of the video memory is programmable to three different starting addresses for compatibility with previous video adapters. BIOS will program the VGA appropriately during a video mode set.

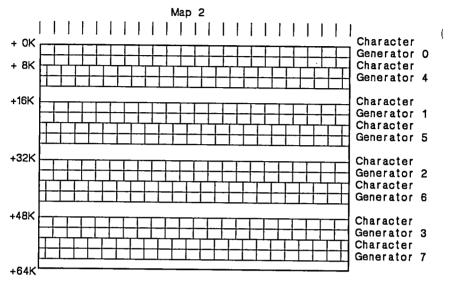

In alphanumeric modes, the system microprocessor writes ASCII character code and attribute data to the video memory maps 0 and 1. respectively. The character generator is stored in video map 2 and is loaded by BIOS during an alphanumeric video mode set. BIOS downloads the character generator data (character generator = font = character set) from system ROM. Three fonts are contained in ROM. Two fonts contain dot patterns identical to those provided by the IBM Monochrome Display Adapter, the IBM Color/Graphics Monitor Adapter, and the IBM Enhanced Graphics Adapter. The third font is an 8 x 16 character font. Up to eight 256-character fonts can be loaded into video memory map 2 at a time (the IBM Enhanced Graphics Adapter allows up to four fonts). A BIOS interface exists to load user-defined fonts. As on the IBM Enhanced Graphics Adapter, a register selects which font is actually used to form characters. Also, as on the IBM Enhanced Graphics Adapter, the intensity bit in the attribute byte may be redefined as a switch between two 256-character fonts. This allows 512 characters to be displayed on the screen at one time. See "Character Map Select Register" on page 3-61 and "RAM-Loadable Character Generator" on page 3-97.

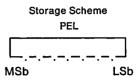

The VGA formats the information stored in video memory into an 8-bit digital value that is sent to the video DAC. This 8-bit value allows access to a maximum of 256 registers inside the video DAC. For example, in the two-color graphics modes, only two different 8-bit values would be presented to the video DAC. In the 256-Color Graphics mode, 256 different 8-bit values would be presented to the video DAC. Each register inside the video DAC contains a color value that is selected from a choice of over 256,000 colors.

The video DAC outputs three analog color signals (red, green, and blue) that are sent to the display connector. The monochrome analog display uses only the green analog output. This output is used to determine the shade of gray that is displayed.

The video subsystem supports attachment of only 31.5 KHz direct-drive analog displays. Other IBM displays are not supported because they have digital interfaces, or have a different horizontal sweep frequency.

A BIOS call enables or disables the VGA. Disable means that the VGA will not respond to video memory or I/O reads or writes. The contents of registers and video memory are preserved with the values present when the disable is invoked. Because of this, the VGA continues to generate valid video output if it was doing so before it was disabled.

Compatibility with other hardware is best achieved by using the BIOS interface whenever possible. If an application is forced to write directly to the VGA, the following rules should be followed:

- To program address registers, all currently reserved bits should be set to 0 to maximize compatibility with other hardware.

- To program data registers, all currently reserved bits should be read out and written back unmodified to maximize compatibility with other hardware.

Previous video adapters required that the video mode used correspond to the display attached. For example, the IBM Enhanced Graphics Adapter required that the Enhanced Color Display be attached to run mode hex 3\*, and required that the monochrome display be attached to run mode hex 7. All the modes supported by the VGA are supported by the IBM 31.5 KHz direct-drive analog displays. Colors are displayed as shades of gray when the monochrome analog display is connected. Circuitry on the system board detects which type of analog display is connected (color or monochrome). BIOS maps (sums) the colors into shades of gray.

(

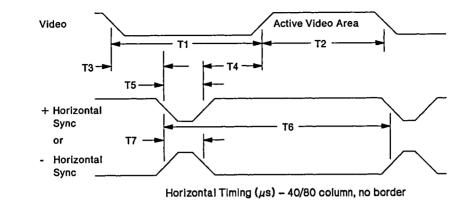

Figure 3-10 on page 3-17 is a block diagram of the video subsystem on the system board.

Figure 3-10. Video Subsystem Block Diagram

### **VGA Components**

Most of the logic for the VGA is contained in one module. This module contains all the circuits necessary to generate the timing for the video memory and generates the video information that goes to the video DAC.

# **BIOS ROM**

Software support is provided by video BIOS. Video BIOS is part of the system BIOS. BIOS is contained in the read-only memory (ROM) on the system board. This ROM BIOS contains the character generators and the control code to run the video subsystem.

# **Support Logic**

Two clock sources (25.175 MHz and 28.322 MHz) provide the dot rate. The clock source is selected by setting a bit in a sequencer register. This is done by BIOS when a mode set is done.

The digital video output is sent to the video digital-to-analog converter (DAC), which contains a color look-up table. Three analog signals (red, green, blue) are output from the DAC and are sent to the display. (See "Attribute Controller" on page 3-21.) The sync signals to the monitor are TTL levels. The analog video signals are 0 to 0.7 volts.

The maximum number of colors displayed is 16 out of 256K, except mode hex 13, which can display 256 out of 256K. The maximum number of shades of gray is 16 out of 64, except mode hex 13, which can display 64 out of 64 shades of gray.

ĺ

1

### **Video Graphics Array Major Components**

The video graphics array has four major components:

- CRT controller

- Sequencer

- Graphics controller

- Attribute controller.

#### **CRT Controller**

The cathode ray tube (CRT) controller generates horizontal and vertical synchronous timings, addressing for the regenerative buffer, cursor and underline timings, and refresh addressing for the dynamic RAMs.

#### Sequencer

(

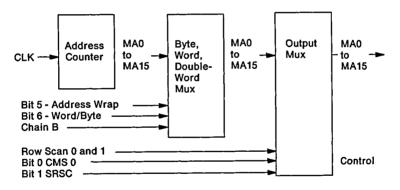

The sequencer generates basic memory timings for the dynamic RAMs and the character clock for controlling regenerative memory fetches. It allows the system microprocessor to access memory during active display intervals by inserting dedicated system microprocessor memory cycles periodically between the display memory cycles. Map Mask registers are available to protect entire memory maps from being changed.

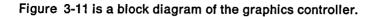

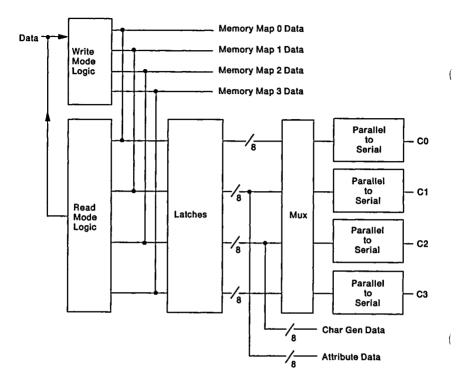

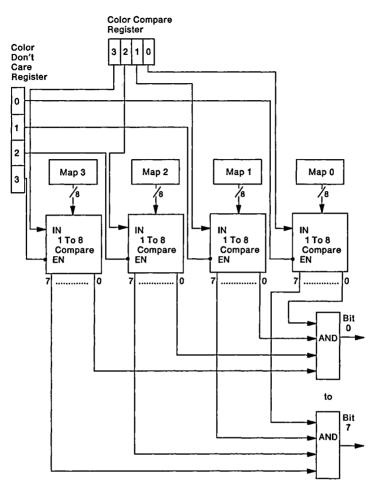

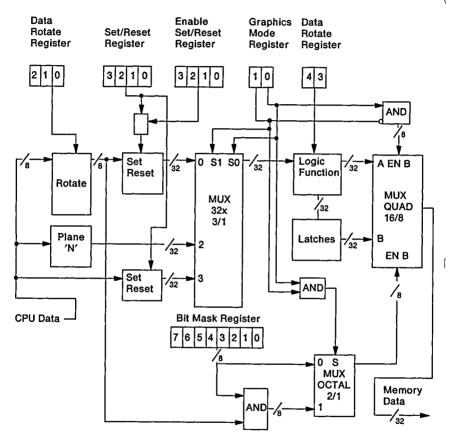

The graphics controller is the interface between video memory and either the attribute controller during active display times or the system microprocessor during video memory reads or writes. During display times, memory data is latched and sent to the attribute controller. In all points addressable (APA) modes, the parallel memory data is converted to serial bit-plane data before being sent. In alphanumeric (A/N) modes, the parallel attribute data is sent directly. During a system microprocessor write or read to video memory, the graphics controller can perform logical operations on the memory data before it reaches video memory or the system microprocessor data bus, respectively. These operations include four logical write modes and two logical read modes. These features allow enhanced operations such as a color-compare read mode. individual bit masking during write modes, 32-bit writes in a single memory cycle, and writing to the display buffer on non-byte boundaries.

(

Figure 3-11. Graphics Controller Block Diagram

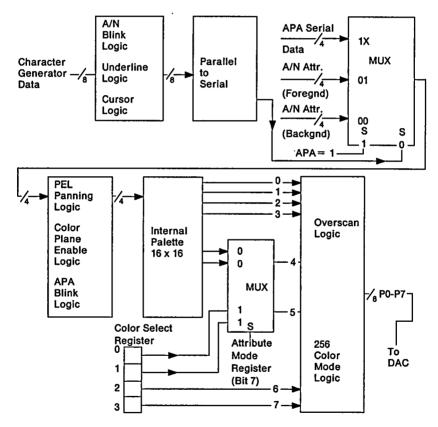

#### **Attribute Controller**

The attribute controller takes in data from video memory through the graphics controller and formats it for display. Incoming attribute data in A/N mode, and serialized bit-plane data in APA mode is converted to an 8-bit output digital color value. Each output color value is selected from an internal color palette of 64 possible colors (except in 256-Color mode). The output color value is sent to the integrated DAC, where it is used as an address into an 18-bit color register whose value is in turn converted to three analog color signals that drive the display. Blinking, underlining, cursor insertion, and PEL panning are also controlled by the attribute controller.

Figure 3-12. Attribute Controller Block Diagram

# **Modes of Operation**

Figure 3-13 describes the modes supported by BIOS on IBM 31.5 KHz direct-drive analog color and monochrome displays.

| Mode<br>(hex)         Alpha<br>Type         Buffer<br>Format         Box<br>Start         Max<br>Size         Vert.<br>Pgs.         PELS           0,1         A/N         16/256K 40 x 25<br>8 8000         8 x 8<br>8 8         8<br>70 Hz         320 x 200<br>640 x 200           2,3         A/N         16/256K 80 x 25<br>8 8000         8 x 8<br>8 8         8<br>70 Hz         320 x 200<br>640 x 200           0*, 1*         A/N         16/256K 40 x 25<br>8 8000         8 x 14<br>8         70 Hz         320 x 3/0<br>8 x 3/0           2*, 3*         A/N         16/256K 40 x 25<br>8 8000         8 x 14<br>8         70 Hz         360 x 400<br>360 x 400           2+, 3+         A/N         16/256K 80 x 25<br>8 8000         8 x 14<br>8         70 Hz         320 x 200<br>320 x 200           6         APA         4/256K 40 x 25<br>8 8000         8 x 8<br>1         70 Hz         320 x 200<br>320 x 200           6         APA         2/256K 80 x 25<br>80000         9 x 16<br>8         70 Hz         720 x 400<br>720 x 400           7         A/N         -         80 x 25<br>80000         9 x 16<br>8         70 Hz         720 x 400           7         A/N         -         80 x 25<br>80000         9 x 16<br>8         70 Hz         640 x 200           7         A/N         -         80 x 25<br>80000         8 x 14<br>8         70 Hz | Figure 3-13. BIOS Video Modes |        |         |          |       |        |       |       |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|---------|----------|-------|--------|-------|-------|-----------|

| Colors           0, 1         A/N         16/256K 40 × 25         B8000         8 × 8         8         70 Hz         320 × 200           2, 3         A/N         16/256K 80 × 25         B8000         8 × 8         8         70 Hz         320 × 200           0', 1*         A/N         16/256K 80 × 25         B8000         8 × 8         8         70 Hz         320 × 200           0', 1*         A/N         16/256K 40 × 25         B8000         8 × 14         8         70 Hz         320 × 3/0           2', 3*         A/N         16/256K 80 × 25         B8000         8 × 14         8         70 Hz         360 × 400           2+, 3 +         A/N         16/256K 40 × 25         B8000         9 × 16         8         70 Hz         320 × 200           6         APA         4/256K 40 × 25         B8000         9 × 16         8         70 Hz         320 × 200           7         A/N         16/256K 80 × 25         B8000         9 × 16         8         70 Hz         320 × 200           7         A/N         -         80 × 25         B0000         9 × 14         8         70 Hz         640 × 200           7 +         A/N         -         80 × 25                                                                                                                                                                                        | Mode                          |        | Alpha   | Buffer   | Box   |        |       |       |           |

| 0, 1 A/N 16/256K 40 x 25 B8000 8 x 8 8 70 Hz 320 x 200<br>2, 3 A/N 16/256K 80 x 25 B8000 8 x 8 8 70 Hz 640 x 200<br>0°, 1° A/N 16/256K 40 x 25 B8000 8 x 14 8 70 Hz 320 x 3/0<br>2°, 3° A/N 16/256K 80 x 25 B8000 8 x 14 8 70 Hz 640 x 350<br>0°, 1° A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2°, 3° A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2°, 3° A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2°, 3° A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2°, 3° A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>7 A/N - 80 x 25 B0000 9 x 14 8 70 Hz 720 x 350<br>7° A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 80 x 25 A0000 8 x 8 4 70 Hz 320 x 200<br>F APA - 80 x 25 A0000 8 x 8 4 70 Hz 640 x 250<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>12 APA 16/256K 80 x 25 A0000 8 x 16 1 60 Hz 640 x 480<br>13 APA 256/256K40 x 25 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                               | (nex)                         | туре   | Format  | Start    | Size  | rgs.   | Freq. | PELS  |           |

| 2, 3 A/N 16/256K 80 x 25 B8000 8 x 8 8 70 Hz 640 x 200<br>0*, 1* A/N 16/256K 40 x 25 B8000 8 x 14 8 70 Hz 320 x 3/0<br>2*, 3* A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+, 3+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+, 3+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+, 3+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 9 x 16 8 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>7 A/N - 80 x 25 B8000 9 x 16 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 A0000 8 x 8 8 70 Hz 720 x 400<br>D APA 16/256K 80 x 25 A0000 8 x 8 8 70 Hz 320 x 200<br>E APA 16/256K 80 x 25 A0000 8 x 8 4 70 Hz 640 x 200<br>F APA - 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>12 APA 16/256K 80 x 30 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                      |                               | Colors |         |          |       |        |       |       |           |

| 0*, 1* A/N 16/256K 40 x 25 B8000 8 x 14 8 70 Hz 320 x 3/0<br>2*, 3* A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 640 x 350<br>0+, 1+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+, 3+ A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>4, 5 APA 4/256K 40 x 25 B8000 9 x 16 8 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 9 x 14 8 70 Hz 320 x 200<br>7 A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 A0000 8 x 8 8 70 Hz 320 x 200<br>E APA 16/256K 80 x 25 A0000 8 x 8 4 70 Hz 320 x 200<br>F APA - 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>12 APA 16/256K 80 x 30 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0, 1                          | A/N    | 16/256K | 40 x 25  | B8000 | 8 x 8  | 8     | 70 Hz | 320 x 200 |

| 2*, 3* A/N 16/256K 80 x 25 B8000 8 x 14 8 70 Hz 640 x 350<br>0+, 1+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+, 3+ A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>4, 5 APA 4/256K 40 x 25 B8000 8 x 8 1 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 9 x 14 8 70 Hz 720 x 350<br>7 A/N - 80 x 25 B0000 9 x 14 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 A0000 8 x 8 8 70 Hz 720 x 400<br>E APA 16/256K 80 x 25 A0000 8 x 8 70 Hz 720 x 350<br>F APA - 80 x 25 A0000 8 x 8 70 Hz 720 x 350<br>F APA - 80 x 25 A0000 8 x 8 4 70 Hz 320 x 200<br>F APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>12 APA 16/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>13 APA 256/256K40 x 25 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2, 3                          | A/N    | 16/256K | 80 x 25  | B8000 | 8 x 8  | 8     | 70 Hz | 640 x 200 |

| 0+,1+ A/N 16/256K 40 x 25 B8000 9 x 16 8 70 Hz 360 x 400<br>2+,3+ A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>4,5 APA 4/256K 40 x 25 B8000 8 x 8 1 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 8 x 8 1 70 Hz 640 x 200<br>7 A/N - 80 x 25 B8000 9 x 14 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 A0000 8 x 8 4 70 Hz 720 x 400<br>D APA 16/256K 80 x 25 A0000 8 x 8 4 70 Hz 640 x 200<br>F APA - 80 x 25 A0000 8 x 8 4 70 Hz 640 x 200<br>F APA - 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>12 APA 16/256K 80 x 30 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0*, 1*                        | A/N    | 16/256K | 40 x 25  | B8000 | 8 x 14 | 8     | 70 Hz | 320 x 3/0 |

| 2+, 3+ A/N 16/256K 80 x 25 B8000 9 x 16 8 70 Hz 720 x 400<br>4, 5 APA 4/256K 40 x 25 B8000 8 x 8 1 70 Hz 320 x 200<br>6 APA 2/256K 80 x 25 B8000 8 x 8 1 70 Hz 320 x 200<br>7 A/N - 80 x 25 B0000 9 x 14 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 350<br>7+ A/N - 80 x 25 B0000 9 x 16 8 70 Hz 720 x 400<br>D APA 16/256K 40 x 25 A0000 8 x 8 4 70 Hz 320 x 200<br>E APA 16/256K 80 x 25 A0000 8 x 8 4 70 Hz 640 x 200<br>F APA - 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>10 APA 16/256K 80 x 25 A0000 8 x 14 2 70 Hz 640 x 350<br>11 APA 2/256K 80 x 30 A0000 8 x 16 1 60 Hz 640 x 480<br>12 APA 16/256K 40 x 25 A0000 8 x 8 1 70 Hz 320 x 200<br>* Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2*, 3*                        | A/N    | 16/256K | 80 x 25  | B8000 | 8 x 14 | 8     | 70 Hz | 640 x 350 |

| 4, 5       APA       4/256K       40 x 25       B8000       8 x 8       1       70 Hz       320 x 200         6       APA       2/256K       80 x 25       B8000       8 x 8       1       70 Hz       320 x 200         7       A/N       -       80 x 25       B8000       9 x 14       8       70 Hz       720 x 350         7+       A/N       -       80 x 25       B0000       9 x 16       8       70 Hz       720 x 350         7+       A/N       -       80 x 25       B0000       9 x 16       8       70 Hz       720 x 400         D       APA       16/256K 40 x 25       A0000       8 x 8       8       70 Hz       640 x 200         F       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         10       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         11       APA       2/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         12       APA       16/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         13       APA <td< td=""><td>0+,1+</td><td>A/N</td><td>16/256K</td><td>40 x 25</td><td>B8000</td><td>9 x 16</td><td>8</td><td>70 Hz</td><td>360 x 400</td></td<>                                                                                                                                       | 0+,1+                         | A/N    | 16/256K | 40 x 25  | B8000 | 9 x 16 | 8     | 70 Hz | 360 x 400 |

| 6       APA       2/256K       80 x 25       B8000       8 x 8       1       70 Hz       640 x 200         7       A/N       -       80 x 25       B0000       9 x 14       8       70 Hz       720 x 350         7+       A/N       -       80 x 25       B0000       9 x 14       8       70 Hz       720 x 350         7+       A/N       -       80 x 25       B0000       9 x 16       8       70 Hz       720 x 400         D       APA       16/256K 40 x 25       A0000       8 x 8       8       70 Hz       640 x 200         F       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         10       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         11       APA       2/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         12       APA       16/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         13       APA       256/256K40 x 25       A0000       8 x 8       1       70 Hz       320 x 200         *       Enhanced modes (EGA) <td< td=""><td>2+,3+</td><td>A/N</td><td>16/256K</td><td>80 x 25</td><td>B8000</td><td>9 x 16</td><td>8</td><td>70 Hz</td><td>720 x 400</td></td<>                                                                                                                              | 2+,3+                         | A/N    | 16/256K | 80 x 25  | B8000 | 9 x 16 | 8     | 70 Hz | 720 x 400 |

| 7       A/N       -       80 x 25       B0000       9 x 14       8       70 Hz       720 x 350         7 +       A/N       -       80 x 25       B0000       9 x 16       8       70 Hz       720 x 400         D       APA       16/256K 40 x 25       A0000       8 x 8       8       70 Hz       320 x 200         E       APA       16/256K 80 x 25       A0000       8 x 8       4       70 Hz       640 x 200         F       APA       -       80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         10       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         11       APA       2/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         12       APA       16/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         13       APA       256/256K40 x 25       A0000       8 x 8       1       70 Hz       320 x 200         *       Enhanced modes (EGA)       *       Enhanced modes (EGA)       5       5       5       5                                                                                                                                                                                                                                                                                                                          | 4, 5                          | APA    | 4/256K  | 40 x 25  | B8000 | 8 x 8  | 1     | 70 Hz | 320 x 200 |

| 7+       A/N       -       80 x 25       B0000       9 x 16       8       70 Hz       720 x 400         D       APA       16/256K 40 x 25       A0000       8 x 8       8       70 Hz       320 x 200         E       APA       16/256K 80 x 25       A0000       8 x 8       4       70 Hz       640 x 200         F       APA       -       80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         10       APA       16/256K 80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         11       APA       2/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         12       APA       16/256K 80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         13       APA       256/256K40 x 25       A0000       8 x 8       1       70 Hz       320 x 200         * Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               | APA    | 2/256K  | 80 x 25  | B8000 | 8 x 8  | 1     | 70 Hz | 640 x 200 |

| D         APA         16/256K         40 x 25         A0000         8 x 8         8         70 Hz         320 x 200           E         APA         16/256K         80 x 25         A0000         8 x 8         4         70 Hz         640 x 200           F         APA         -         80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           10         APA         16/256K         80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           11         APA         2/256K         80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           12         APA         16/256K 80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           *         Enhanced modes (EGA)         EGA)         4000         8 x 8         1         70 Hz         320 x 200                                                                                                                                                                                                                                                                                                                                                                       | 7                             | A/N    | -       | 80 x 25  | B0000 | 9 x 14 | 8     | 70 Hz | 720 x 350 |

| E         APA         16/256K         80 x 25         A0000         8 x 8         4         70 Hz         640 x 200           F         APA         -         80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           10         APA         16/256K         80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           11         APA         2/256K         80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           12         APA         16/256K 80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           * Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7+                            | A/N    | -       | 80 x 25  | B0000 | 9 x 16 | 8     | 70 Hz | 720 x 400 |

| F         APA         -         80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           10         APA         16/256K 80 x 25         A0000         8 x 14         2         70 Hz         640 x 350           11         APA         2/256K 80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           12         APA         16/256K 80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           * Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D                             | APA    | 16/256K | 40 x 25  | A0000 | 8 x 8  | 8     | 70 Hz | 320 x 200 |

| 10       APA       16/256K       80 x 25       A0000       8 x 14       2       70 Hz       640 x 350         11       APA       2/256K       80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         12       APA       16/256K       80 x 30       A0000       8 x 16       1       60 Hz       640 x 480         13       APA       256/256K40 x 25       A0000       8 x 8       1       70 Hz       320 x 200         *       Enhanced modes (EGA)       *       *       *       *       *       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Е                             | APA    | 16/256K | 80 x 25  | A0000 | 8 x 8  | 4     | 70 Hz | 640 x 200 |

| 11         APA         2/256K         80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           12         APA         16/256K         80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           * Enhanced modes (EGA)         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *                                                                                                                                                                                                                                                  | F                             | APA    | -       | 80 x 25  | A0000 | 8 x 14 | 2     | 70 Hz | 640 x 350 |

| 12         APA         16/256K         80 x 30         A0000         8 x 16         1         60 Hz         640 x 480           13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           * Enhanced modes (EGA)         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *         *                                                                                                                                                                                                                                                         | 10                            | APA    | 16/256K | 80 x 25  | A0000 | 8 x 14 | 2     | 70 Hz | 640 x 350 |

| 13         APA         256/256K40 x 25         A0000         8 x 8         1         70 Hz         320 x 200           * Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                            | APA    | 2/256K  | 80 x 30  | A0000 | 8 x 16 | 1     | 60 Hz | 640 x 480 |

| * Enhanced modes (EGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                            | APA    | 16/256K | 80 x 30  | A0000 | 8 x 16 | 1     | 60 Hz | 640 x 480 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                            | APA    | 256/256 | <40 x 25 | A0000 | 8 x 8  | 1     | 70 Hz | 320 x 200 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | * Enhanced modes (EGA)        |        |         |          |       |        |       |       |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |        |         |          |       |        |       |       |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |        |         | Y        |       |        |       |       |           |

When the color display is used, each color is selected from a palette of over 256,000 colors.

When the monochrome display is used, the colors are displayed as shades of gray. Each shade of gray is selected from a palette of 64 shades.

Modes hex 0 through 6 emulate the support provided by the IBM Color/Graphics Monitor Adapter.

Modes hex 0, 2, and 4 are identical to modes hex 1, 3, and 5, respectively. On the IBM Color/Graphics Monitor Adapter there is a difference in these modes. In modes hex 0, 2, and 4, the color burst was turned off. Color burst is not provided by the video subsystem. Mode hex 3 + is the default mode with an analog color display attached to the system. Mode hex 7 + is the default mode with an analog monochrome display attached to the system.

(

Mode hex 7 emulates the support provided by the IBM Monochrome Display Adapter.

Modes hex 0\*, 1\*, 2\*, 3\*, D, E, F, and 10 emulate the support provided by the IBM Enhanced Graphics Adapter.

Double-scan means that each horizontal scan line is displayed twice. This is used for 200-line modes, which are displayed as 400 lines. Border support depends on the BIOS mode selected. Figure 3-14 shows double-scan and border support.

| Figure  | 3-14. BIOS Dou   | ble-Scan and Border Supp | port |

|---------|------------------|--------------------------|------|

| Mode    | Double           | Border                   |      |

| (hex)   | Scan             | Support                  |      |

|         |                  |                          |      |

| 0, 1    | Yes              | No                       |      |

| 2, 3    | Yes              | Yes                      |      |

| 0*, 1*  | No               | No                       |      |

| 2*, 3*  | No               | Yes                      |      |

| 0+,1+   | No               | No                       | 1    |

| 2+,3+   | No               | Yes                      | /    |

| 4, 5    | Yes              | No                       |      |

| 6       | Yes              | Yes                      |      |

| 7       | No               | Yes                      |      |

| 7+      | No               | Yes                      |      |

| D       | Yes              | No                       |      |

| E       | Yes              | Yes                      |      |

| F       | No               | Yes                      |      |

| 10      | No               | Yes                      |      |

| 11      | No               | Yes                      |      |

| 12      | No               | Yes                      |      |

| 13      | Yes              | Yes                      |      |

|         |                  |                          |      |

| * Enhan | ced modes (EGA)  |                          |      |

| + Enha  | nced modes (VGA) |                          |      |

|         |                  |                          |      |

#### **Display Support**

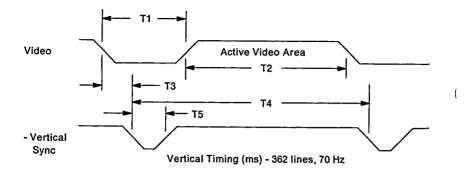

The video subsystem supports attachment of 31.5 KHz horizontal sweep frequency direct-drive analog displays. These displays have a vertical sweep frequency capability of 60 to 70 cycles per second, providing extended color and sharpness and reduced flicker in most modes. Other IBM displays are not supported because they have digital interfaces, or have a different horizontal and vertical sweep frequency. Figure 3-15 summarizes the analog display characteristics.

| irect-Drive Analog Dis | plays                                                                      |

|------------------------|----------------------------------------------------------------------------|

| Color                  | Monochrome                                                                 |

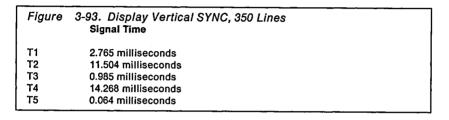

| 31.5 KHz               | 31.5 KHz                                                                   |

| 60 to 70 Hz            | 60 to 70 Hz                                                                |

| 28 MHz                 | 28 MHz                                                                     |

| 256/256K Maximum       | 64/64 Shades Gray                                                          |

| 720 PELs               | 720 PELs                                                                   |

| 480 PELs               | 480 PELs                                                                   |

|                        |                                                                            |

|                        | Color<br>31.5 KHz<br>60 to 70 Hz<br>28 MHz<br>256/256K Maximum<br>720 PELs |

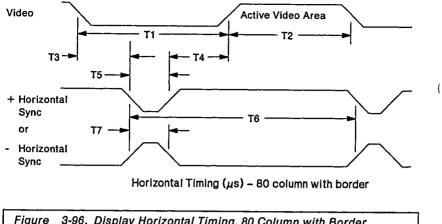

Since both color and monochrome displays run at the same sweep rate, all modes work on either type. The vertical size of the display is controlled by the polarity of the vertical and horizontal sync pulses. This is done so that 350, 400, or 480 lines can be displayed without adjusting the display. (See "Display Connector Timing (SYNC Signals)" on page 3-105.)

### Video Subsystem Programmable Option Select

The video subsystem supports Programmable Option Select (POS). When the POS sleep bit is set, the video subsystem does not respond to any memory or I/O reads or writes. Video is still generated if the video subsystem is programmed to do so. POS must be enabled for video subsystem operation.

The implementation of POS for the video subsystem is as follows:

- When in Setup mode (I/O address hex 0094, bit 5 equals 0), the VGA responds to a single option select byte at I/O address hex 0102 and treats the LSB (bit 0) of that byte as the VGA sleep bit. When the LSB is 0, the VGA does not respond to commands, addresses, or data on the data bus. When the LSB is 1, the VGA responds. If the VGA was set up and is generating video output when the LSB is set to 0, the output is still generated.

- The VGA responds only to address hex 0102 when in the Setup mode. No other addresses are valid at that time. Conversely, the VGA ignores address hex 0102 when in the Enabled mode (I/O address hex 0094, bit 5 equals 1), and decodes normal I/O and memory addresses.

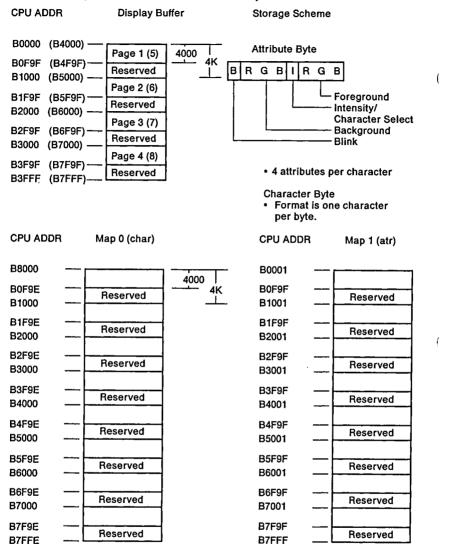

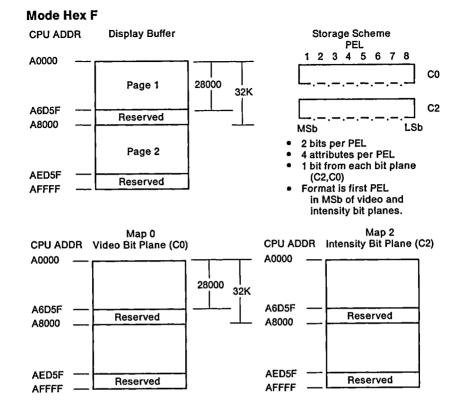

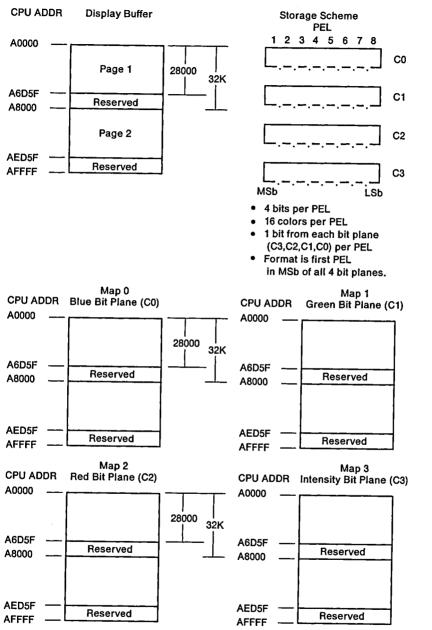

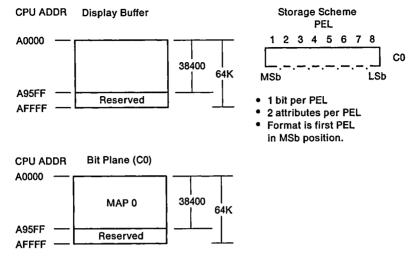

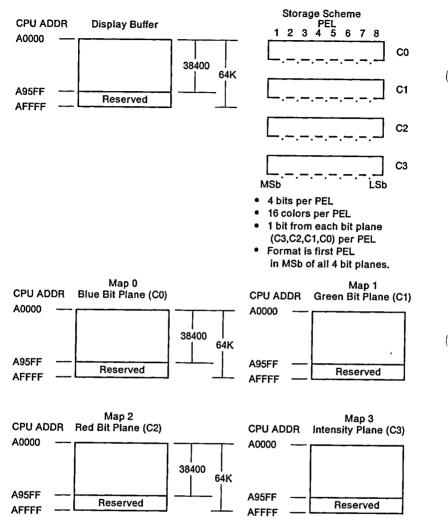

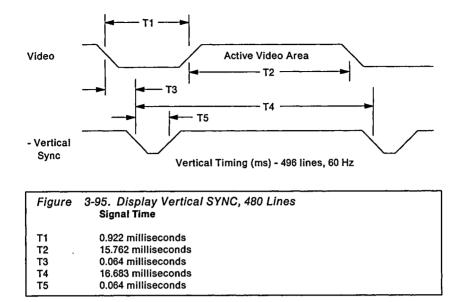

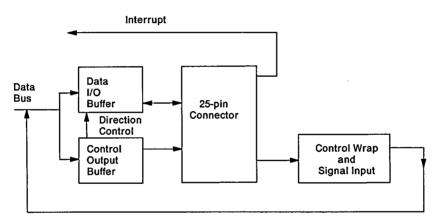

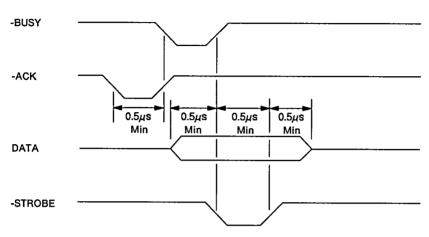

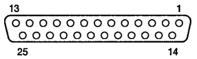

(